The consequence of such a transition is that the output of g 4 makes a 0 → 1 transition which is transferred to one of the inputs of both g 1 and g 3 without affecting their outputs.

If a change in D from 1 → 0 takes place after the hold time has elapsed and while the clock is still high, there will be no further change in the flip-flop output. The changes taking place in the circuit after the clock transition from 0 → 1 are recorded in Figure 6.21(c). It is essential that there should be no change in D during this period. The time taken for S ¯ to change 1 → 0 is the hold time and is equal to the gate delay of g 2. This is because the lower input of g 3 made a 1 → 0 transition during the set-up time. It should be noticed that there is no change in R ¯ as a consequence of the clock going high. The change in S ¯ initiates a change of state in the output latch and Q makes a 0 → 1 transition followed by a 1 → 0 transition in Q ¯. The inference is that there should be no change in Ck until after the elapse of the set-up time.Īfter the set-up time, the clock is allowed to go high, and as a consequence the output of g 2, S ¯, makes a 1 → 0 transition. The time delay before this change occurs is equal to the sum of the gate delays g 4 and g 1 and is the set-up time for the flip-flop.

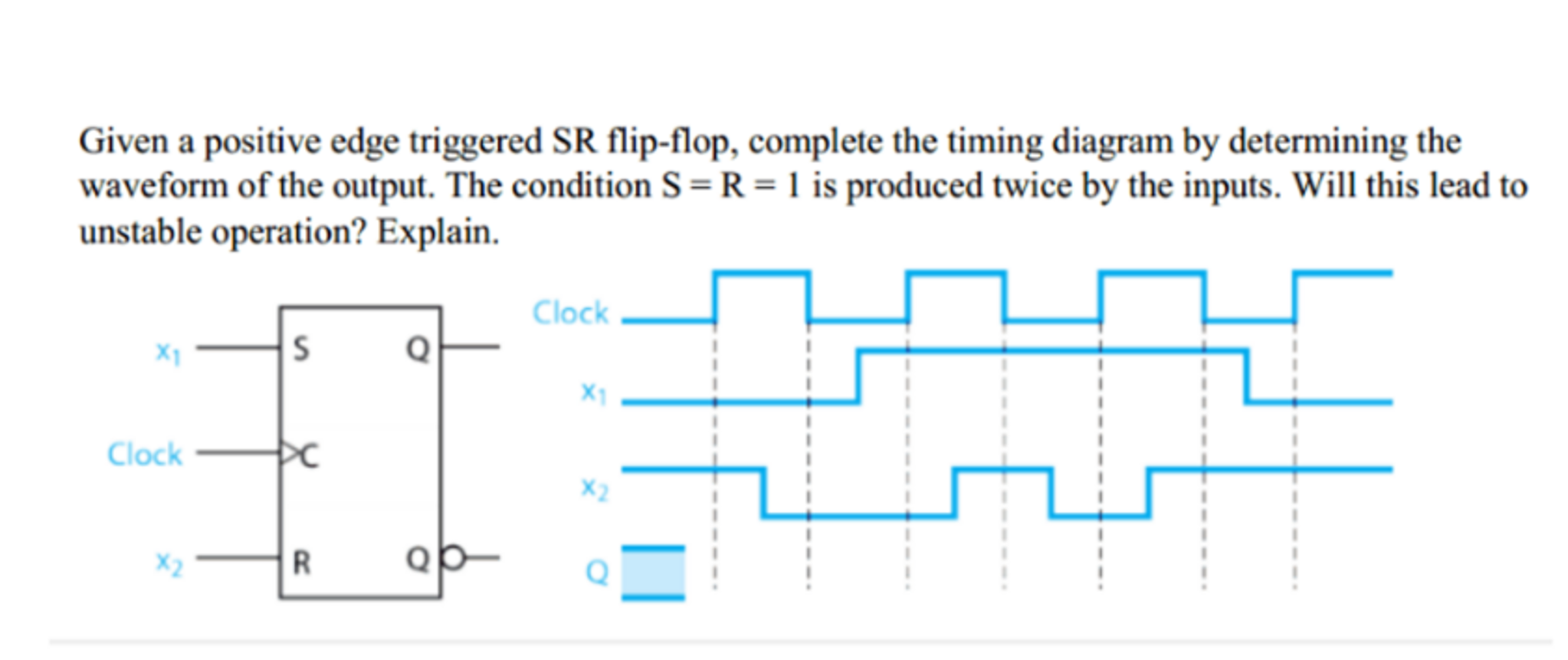

When the data D is changed from 0 → 1 during the asynchronous period then the output of g 4 changes from 1 → 0 which initiates a 0 → 1 transition at the output of g 1 and that change is transferred to the input of g 2 as shown in Figure 6.21(b). If additionally D = 0, then the remaining signals at different parts of the circuit can easily be determined, and they have been inserted in Figure 6.21(b). In order to maintain the output latch in a stable state, both S ¯ and R ¯ must be held at 1 and this is achieved when the clock Ck = 0 since the outputs of g 2 and g 3 are then 1.

The output latch is formed by gates g 5 and g 6. The three latches are interconnected as shown in Figure 6.21(b), with g 1 and g 2 comprising one latch while g 3 and g 4 comprise a second latch. The diagram shows the effect of a 0 → 1 transition on the D line (c) Effect of a 0 → 1 transition on the clock line (a) The basic S ¯ R ¯ flip-flop (b) Edge triggered flip-flop.

0 kommentar(er)

0 kommentar(er)